ニュース

「11nmプロセスまでは自社だけで実現できる」。インテル,製造開発部門のロードマップを披露。筑波本社のラボも一部公開に

今回のメインテーマは,インテルの製造開発部門。直接的なPCゲームとの関連はまったくないが,技術的にはかなり興味深いものだったので,特別にレポートしてみたいと思う。

Intelの屋台骨を支える製造開発部門,

その現状まとめ

|

| 阿部剛士氏(インテル 取締役 技術開発・製造技術本部 本部長) |

|

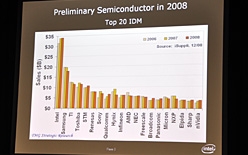

| 阿部氏が示した,(半導体受託製造企業を除く)半導体企業の売り上げランキング,2008年版。TMGは,ダントツの首位を走るIntelの屋台骨を支えるグループというわけだ |

阿部氏の所属する技術開発・製造技術部(Technology and Manufacturing Group,以下TMG)は,全体で8万4000人ほどいるIntel社員のうち,半数以上を占める4万8000人という大所帯。その名称どおり,「Fab」(ファブ)と呼ばれる製造工場や,製造に関連した技術開発に携わる部門だ。

「Fabのない日本に,なぜTMGが存在しているのか?」という疑問はもっともだが,これについて氏は,「日本には,有数のサプライヤーが多くあるから」と説明する。氏のいう「サプライヤー」とは,半導体製造装置やテスト装置,素材など,IntelがCPUやチップセットなどを作るために必要な機械/素材メーカーのこと。「ムーアの法則を下から支える日本のサプライヤーは大切なパートナー」(阿部氏)で,そういった国内メーカーとの連絡を取るために,TMGのスタッフが日本に常駐しているとのこと。国内には,およそ100名のスタッフがいるようだ。

|

Intelは新しい製造技術を,米オレゴン州にある「D1D」というFabで開発する。そして,それが安定した段階で,それをそっくりそのまま,別の場所にコピーするという,「Copy exactly」ポリシーを採用している。「新しいプロセス技術が“固まる”には,1年から1年半が必要」(阿部氏)で,それが済み次第,D1Dで確立した技術を,工程の機材レイアウトや,それこそ装置のリビジョンまで,完全にコピーしていくのだ。それにより,現在は,米国内3か所,イスラエルに1か所の計4か所で,45nmプロセス技術に基づいた半導体の製造が行われている。

ちなみにIntelは現在,Fabをアジアで展開する計画の途上にあり,中国の大連市にFab 68を建設中であるほか,ベトナムのホーチミン市にも「相当大きい規模の」(阿部氏)をFabを計画しているとした。

「2桁台の製造プロセスは,Intelだけで行ける」

これからは後工程にスポットライトが当たると予告

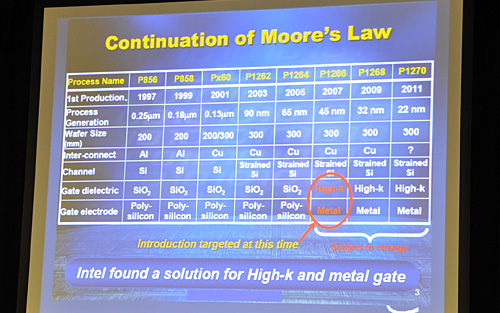

ゲートの絶縁にはHigh-k素材が,また電極にはメタルが使用されている。

ゲートというのは,トランジスタのスイッチ機能を実現する部分で,LSIに使用されるMOSFETが誕生した当時からずっと,電極には多結晶シリコン(Poly-silicone)が,また絶縁素材には酸化シリコン(SiO2)がそれぞれ使用されてきた。このゲートはまさにトランジスタがトランジスタとして機能するキモの部分だけに,阿部氏は「ゲートを変えると何が起こるか分からない」と述べ,素材の変更は大きなチャレンジだったとした。

実際,High-kメタルゲートは,「10年以上前から仕込みが始まっていた」(阿部氏)というほど,長く研究開発が進められてきたそうで,ようやく,45nmプロセスで実用化されたわけである。

|

次の世代はどうなるだろうか?

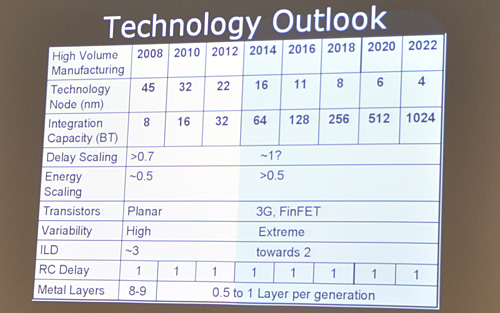

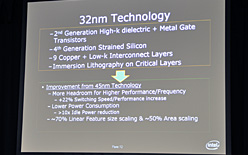

阿部氏は下のスライドを示したうえで,「TMGでは,2桁(ナノメートル)のうちは,Intelだけで,技術的にも財務的にも行けるのではないかと考えている」と,かなり強気な見通しを語る。

Intelは最近「Tick-Tock」戦略に基づき,2年ごとに半導体の製造プロセスを大きくシュリンクさせているが,2016年に量産が始まる予定の16nmプロセス技術までは,“自前”でなんとかできると,ある程度の予測ができているのだろう。

|

では,1桁台プロセス時代はどうなってしまうのか。ゲートが“原子数個”といった大きさになると,諸般の事情からゲートとして機能しなくなってしまう。いわゆる物理的な限界を迎えるのだが,それに向けたIntelのスタンスは「限界が来るまでは(このまま)がんばろう」というものだそうだ。

半導体企業の多くは,先端プロセス技術に対応したFabを自社だけで抱えられなくなってきている。それだけに,「限界が来るまでは,自社でなんとかする」という姿勢は,実に対照的なものといえる。

|

ここでいう前工程とは,シリコンにLSIを作り込んでダイを製造する工程のことで,平たく言えばプロセス技術そのもの。対する後工程というのは,出来上がったダイが正常に機能するかテスト行い,ダイを,CPUソケットなどに装着できる「パッケージ」に収める工程のことだ。

「ピン数が増える一方,小さなパッケージが求められるようになっているため,後工程は二重苦三重苦」(同氏)。どうしても,プロセス技術がスポットライトを浴びがちだが,今後は,これまであまり注目されていなかった後工程でも,大きな革新が必要になるという。

実際,TMGでは現在,さまざまなパッケージを検討しており,なかには「(従来の常識からあまりにも外れているため)ウソ!? というようなものもある」と阿部氏。なかなか期待が高まるが,それが姿を見せるのは,おそらく早くても5〜6年先の話になるはずだ。

32nmは「何の問題もなく立ち上がる」

新興市場が今後のカギに

|

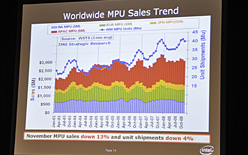

ただし、半導体業界が順風満帆かというとそうではない。昨年からの未曾有の経済危機からの影響は脱しつつあるが,MPUの単価は下がり続けているという。

|

また,「Emerging Market」(エマージングマーケット)と呼ばれる新興市場では,成熟市場と比べて労働者一人ひとりの収入が低いため,低価格な製品が強く求められているが,こうした市場にも「進出していかざるを得ない」と氏は述べる。

市場で求められている低価格な製品を実現するためにはコスト削減が欠かせないが,阿部氏によると,Intelはこれまで,「湯水のようにお金を使う企業」だったそうだが,これからはコスト削減にも積極的に取り組んでいくと述べていた。

筑波本社のラボがちょっとだけ公開に

〜PCメーカーの厳しい要求に対応

|

|

今回,報道関係者に公開されたのは,クライアントPC,UMPC,サーバーのラボ。残念ながら,写真の撮影は許可されなかったため,本文と対応した写真はお見せできないが,今回は三つの中から,4Gamer読者と最も関連が深いデスクトップPCのラボについて,見てきたものを文字ベースでお伝えしたい。

さて,クライアントPCのラボでは,主にPCの熱,電圧(≒消費電力),音に関して重点的に試験を行い,Intel/インテルの重要な顧客である国内PCメーカーの製品設計・開発を支援しているという。

ラボでは実際に,Core i7プロセッサを用いて「Intel Turbo Boost Technology」(以下,Turbo Boost)のデモが行われた。ここでは,Intelの内部ツールを用いて,1コアだけに負荷をかけたとき,1コアだけきっちりと2bin(=ベースクロックで2段階分)上がることが示されたほか,4コアすべてがC6ステートに入ると,コア部の消費電力が0.15〜0.18W(※アンコア部もあるので,これがCPUの消費電力すべてではない)まで落ちることなどが示された。

|

|

実例を写真でお見せできないのが本当に申し訳ないが,インテルの筑波ラボが,PCメーカーと共同で製品開発やトラブル解決に当たっていることは,広報写真からも見て取れるのではなかろうか。海外でのシェアと比べて,国内PCメーカーのIntel製CPU採用率は高いという事実があるが,それは,広告宣伝の効果だけでなく,こうした地道なPCメーカーのサポートにも支えられているのだろう。

- 関連タイトル:

Core i7(LGA1366,クアッドコア)

Core i7(LGA1366,クアッドコア) - この記事のURL:

(C)Intel Corporation