ニュース

Intel,次世代Xeon Phi「Knights Landing」の詳細を公表。SilvermontベースのCPUコア60基以上を1パッケージに集積

|

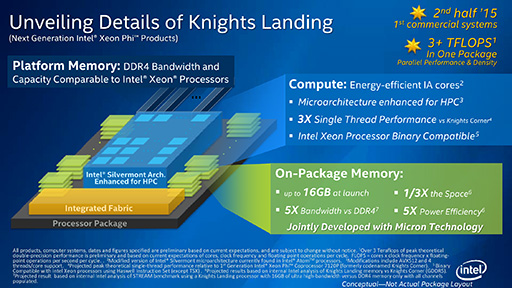

それによると,14nmプロセスで製造されるKnights Landingは,SilvermontアーキテクチャベースのCPUコアにHigh Performance Computing(HPC)分野向けの改良を加えたものを,パッケージ内に60基以上も集積したプロセッサになる。倍精度浮動小数点演算性能は3TFLOPSに,シングルスレッド性能は既存の「Xeon Phi 7100」世代と比べて3倍に達するとのことだ。

さらに,Knights Landingでは,Micron Technologyとの協業により開発されたメモリチップをパッケージ上に最大16GB分搭載し,DDR4メモリ比で5倍の帯域幅とGDDRメモリ比で5倍の電力効率と3倍の密度を実現しているという。なお,CPUコア群とメモリ,およびチップセットとの接続には,「Omni Scale Fabric」と称する高速なインターコネクト技術が使われることも明らかにされている。

|

2013年6月にその存在が公表されたとき予告されていたとおり,Knights Landingには従来のXeon Phiと同じPCI Expressカードタイプの製品だけでなく,独立したCPUとして動作する製品も用意されるとのことだ。

既存のXeon Phiでは,ホストCPUとPCI Expressカード間のデータ転送能力によって性能向上が制約されるという問題があったが,独立して動作するKnights Landingを使えば,この問題は解決できるだろう。

Intelによれば,世界のスーパーコンピュータ性能ランキング「Top500」にランクインしたシステムのうち,18%が既存のXeon Phiを導入しているという。Knights Landingが登場すれば,HPC分野でのXeon Phiシリーズの採用はさらに進むことになりそうだ。

次世代インテル Xeon Phiプロセッサーとインテル Omni Scaleファブリックの組み合わせにより、消費電力を低減しながら前世代製品と比較して最大3倍のパフォーマンスを実現

ニュース・ハイライト

- 2015年後半にHPC向けに提供開始予定の次世代インテル Xeon Phiプロセッサー(開発コード名:Knights Landing)の新マイクロ・アーキテクチャーとメモリー機能の詳細を発表

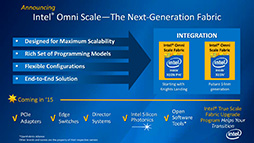

- 高速なデータ転送、レイテンシーの削減、高い効率性の実現に向けて最適化されたエンドツーエンドの相互接続性を備えるインテル Omni Scaleファブリックを発表。2015年から、まず個別のコンポーネントとして提供開始予定で、次世代インテル Xeon Phiプロセッサーと今後提供予定の14nmプロセス技術に基づくインテル Xeonプロセッサーに統合予定

- 最新のTOP500リストに掲載されているスーパーコンピューターの85%にインテルXeonプロセッサーが搭載されるなど、引き続きインテルがHPC領域をリード

インテル コーポレーション(本社:米国カリフォルニア州サンタクララ)は本日、次世代インテル Xeon Phiプロセッサー(開発コード名:Knights Landing)に関する最新情報を発表しました。Knights Landingは、現行のインテル Xeon Phiコプロセッサー製品向けに並列化されたコードを使うことができるので、これまでに投下された投資のメリットをさらに拡張することができます。また、次世代のKnights Landingでは、メモリーと帯域幅を拡張した高速なファブリックがパッケージに内蔵されます。今日、メモリーやファブリックはサーバー内にCPUとは別のコンポーネントとして搭載されており、パフォーマンスや密度に制約を生んでいますが、メモリーやファブリックがパッケージ内に内蔵されることで、こうした制約が低減され、スーパーコンピューターのパフォーマンを大きく改善します。Knights Landingにより、科学的発見のペースがさらに加速するものと期待しています。

インテルの新しいインターコネクト・テクノロジーであるインテル Omni Scaleファブリックは、次世代ハイパフォーマンス・コンピューティング(HPC)の要件に対応できるよう設計されています。インテル Omni Scaleファブリックは、次世代インテル Xeon Phiプロセッサーに加え、将来の汎用インテル Xeonプロセッサーにも統合される予定です。インテル Omni Scaleファブリックのインテルプロセッサーへの統合と、HPC向けに最適化されたアーキテクチャーは、将来にわたってHPC導入に必要とされるパフォーマンス、拡張性、信頼性、消費電力、密度を提供できるよう設計されています。また、インテル Omni Scaleファブリックは、エントリー・レベルから大規模導入まで利用できるよう、パフォーマンスと価格を両立させた設計になっています。

インテル コーポレーション データセンター事業本部 副社長 兼ワークステーション/HPC事業部長のチャールズ・ヴィッチパードは、「インテルは、インテル Omni ScaleファブリックをKnights Landingに統合することでHPCシステムの基盤を再設計します。この統合は、HPC業界に劇的な変化をもたらすとともに、大きなマイルストーンとなるでしょう。Knights Landingは、今日のメモリーとI/Oのパフォーマンスに関する課題に応える最初かつ本物のメニーコアのプロセッサーです。Knights Landingにより、プログラマーは既存のコードと標準的なプログラミング・モデルを活用しながら、幅広いアプリケーションで劇的なパフォーマンス向上を実現できます。Knights Landingが備えるプラットフォーム・デザイン、プログラミング・モデル、バランスの取れたパフォーマンスを通じて、エクサスケールに向けた最初の現実的な手段となります」と述べています。

次世代インテル Xeon Phiプロセッサーの比類なき統合性

次世代インテル Xeon Phiプロセッサー(開発コード名:Knights Landing)は、マザーボードのソケットに直接マウントされるプロセッサーと、PCIeカードとして追加できるスタンドアロンのプロセッサーの2通りで提供される予定です。複数の搭載オプションを提供することにより、プログラミングの複雑性に加え、GPUやアクセラレーターに共通のPCIeデータ転送での帯域幅のボトルネックを取り除くことができます。Knights Landingは出荷時点で最大16ギガバイト(GB)の高帯域幅と、Micron社とのパートナーシップを通じて設計されたメモリー・パッケージを備えており、DDR4メモリーと比較して5倍の帯域幅(*1)に加え、GDDRメモリーと比較して5倍の消費電力効率(*2)、3倍の密度(*2)を実現しています。また、このメモリー・ソリューションとインテル Omni Scaleファブリックとの組み合わせにより、Knights Landingを独立したコンピューティング要素として追加できるため、コンポーネント数を削減でき、省スペースと消費電力の低減が可能になります。

HPC向けに強化されたSilvermontアーキテクチャー・ベースの60以上のコアを搭載したKnights Landingは、3テラFLOPS以上のDP(Double Precision:倍精度浮動小数点演算)パフォーマンス(*3)に加え、現世代製品と比較して3倍のシングルスレッド・パフォーマンス(*4)を提供します。Knights Landingはスタンドアロンのサーバー用プロセッサーとして、インテル Xeonプロセッサー・ベースのプラットフォームが備える容量や帯域幅と同程度のDDR4システムメモリーに対応しているため、大容量のメモリーを使用するアプリケーションを稼働させることができます。Knights Landingはインテル Xeonプロセッサーとバイナリ・レベルでの互換性を備えており(*5)、ソフトウェア開発者はさまざまな既存コードを簡単に再利用できます。

その他のシステム・コンポーネントをアップグレードせずに、対象となる特定のコンポーネントを迅速にアップグレードできる環境を望む顧客は、Knights

Landingとインテル Omni Scaleファブリックのコントローラーを個別のPCIeベースのアドオン・カードとして導入することができます。すでに提供されているインテル True Scaleファブリックと今後提供予定のインテル Omni Scaleファブリックはアプリケーション・レベルでの互換性を備えており、顧客はアプリケーションを変更することなく、新しいインテル Omni Scaleファブリックに移行できます。インテルでは、インテル True Scaleファブリックを購入済みの顧客に、インテル Omni Scaleファブリックにアップグレードできるプログラムを提供予定です。

Knights Landingは、HPCシステム向けに2015年後半からの提供開始が予定されています。今年4月には、米国エネルギー省の国立エネルギー研究科学コンピューティングセンター(National Energy Research Scientific Computing Center、NERSC)が、2016年にHPC向けにKnights Landingを導入することを発表しており、同組織の5,000以上のユーザーと700以上の大規模な科学的プロジェクトで利用される予定です。

ローレンス・バークレー国立研究所のNERSCディレクターであるSudip Dosanjh博士は、「NERSCの次世代スーパーコンピューターであるCoriの開発におけるCrayならびにインテルとのパートナーシップに興奮しています。Coriは9,300以上のKnights Landingで構成され、その利用しやすいプログラミング・モデルを通じて、我々のユーザーにとってエクサスケールへの入り口となるでしょう。我々は、コードの設定にしばしばメモリー帯域幅の制約を受けていますが、Knights Landingのパッケージ化されたメモリーによる高速性能が大きなメリットをもたらしてくれるものと期待しています。NERSCでは、今日のスーパーコンピューターでは実現できない新たな科学的発見が可能になることを楽しみにしています」と述べています。

インテル Omni Scaleファブリックによる新しいファブリック構成とさらなる高速化

インテル Omni Scaleファブリックは、インテルがCrayとQLogicから取得した強固なIPと、インテル独自開発の革新技術の組み合わせで構成されています。同ファブリックには、アダプター、エッジ・スイッチ、ディレクター・スイッチ・システム、オープン・ソースのファブリック・マネジメントとソフトウェア・ツールなど、すべての要素が含まれています。さらに、今日のファブリックにあるディレクター・スイッチで使用されている従来型の電気的トランシーバーを、インテル シリコン・フォトニクスをベースにしたソリューションに置換し、ポート密度の向上や、ケーブルの簡素化、コストの削減(*6)を図ることができます。インテル シリコン・フォトニクスを活用したケーブルやトランシーバーのソリューションは、インテル Omni Scaleファブリックをベースにしたプロセッサーやアダプター・カード、エッジ・スイッチと併用することができます。

スーパーコンピューターでの勢いを持続するインテル

35ペタFLOPSを誇る世界最高性能のシステムである中国の天河二号(Milky Way 2)で、現世代のインテル Xeonプロセッサーとインテル Xeon Phiコプロセッサーが原動力となっています。また、インテル Xeon Phiコプロセッサーは、世界のシステム・メーカーで採用が進み、搭載システムは200超に上ります。

今回発表された第43回TOP500リストに掲載されているスーパーコンピューターのうち85%にインテルのプロセッサーが採用され、さらに新たにリスト入りしたシステムの97%がインテルのプロセッサーを搭載しています。また、インテル初のメニーコア・アーキテクチャー製品であるインテル Xeon Phiコプロセッサーは、提供開始から18ヵ月間で、TOP500にリストされた18%のスーパーコンピューターに採用され、性能向上に貢献しています。レポートの詳細は、http://www.top500.orgをご覧ください。

インテルは、メニーコアの処理向けにアプリケーションを最適化する取り組みとして、世界の大学や研究機関と協力し、インテル パラレル・コンピューティング・センター(IPCC)を30以上、設立しています。現在のインテル Xeon Phiコプロセッサーに対する並列最適化の投資は、次世代製品のKnights Landingへと進展し、標準ベースの共通プログラミング言語を使用した最適化によるリコンパイルの実現に向け、その活動は続けられています。この取り組みのよる進展は徐々に結実しており、新しい機能性の利点を活用できるようになります。

(*1) Projected result based on internal Intel analysis of STREAM benchmark using a Knights Landing processor with 16GB of high-bandwidth versus DDR4 memory only with all channels populated

(*2) Projected results based on internal Intel analysis of Knights Landing’s on-package memory MCDRAM vs Knights Corner’s GDDR5 memory

(*3) Internal and preliminary projections of theoretical double-precision performance measured by Linpack. Based on current expectations of Knights Landing’s cores, clock frequency and floating point operations per cycle.

(*4). Projected peak theoretical single-thread performance relative to

1st Generation Intel Xeon Phi Coprocessor 7120P (formerly code-named Knights Corner)

(*5) Binary Compatible with Intel Xeon processors using Haswell Instruction Set (except TSX - Transactional Synchronization Extensions)

(*6) The TCO or other cost reduction scenarios described in this document are intended to enable you to get a better understanding of how the purchase of a given Intel product, combined with a number of situation-specific variables, might affect your future cost and savings. Circumstances will vary and there may be unaccounted-for costs related to the use and deployment of a given product. Nothing in this document should be interpreted as either a promise of or contract for a given level of costs.”

- 関連タイトル:

Xeon Phi

Xeon Phi - この記事のURL: