ニュース

Intel,次世代Xeon Phi「Knights Landing」を中核にしたHPCシステム「Scalable System Framework」を紹介

|

HPCシステムを構築する要素をまとめたプラットフォーム

Scalable System Framework

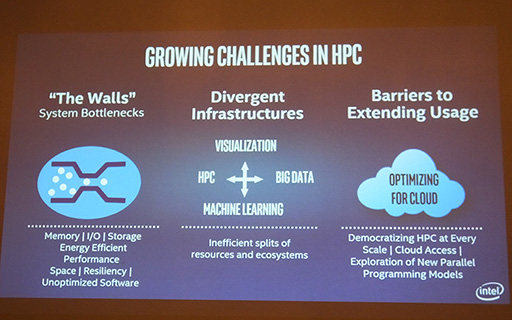

Saleh氏はまず,HPC分野の現状を簡単に説明した。曰く,「HPCは知見やイノベーションの“エネルギー源”」であり,さまざまな分野において,HPCの活用によって問題解決や発見,発明などが行われているとのことだ。そしてHPC分野では,さらに現在,演算性能を向上させるために大きく3つの問題を解決すべく,取り組みが行われているという。

1つは,現状の「HPCシステムに存在するボトルネックの解消」により性能を向上させること。2つめは「インフラの分散」の解消だ。現在,ビッグデータ解析や機械学習,データの可視化といった研究がバラバラに行われていることで,HPCのエコシステムやリソースが分散してしまっていることが問題だという。そして3つめは,クラウドの利用を前提とした,理解しやすい「プログラミングモデルの導入」といった要素だ。

これらがHPCの普及を阻む障壁となっており,さらなる普及のためには,これを解消する必要があるとSaleh氏は述べる。

|

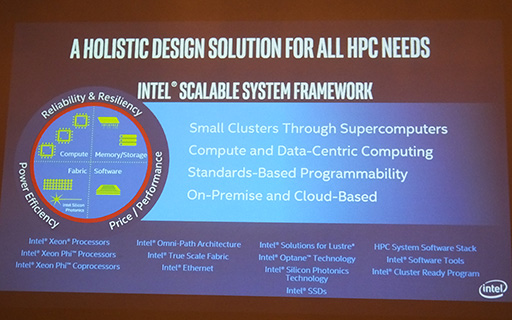

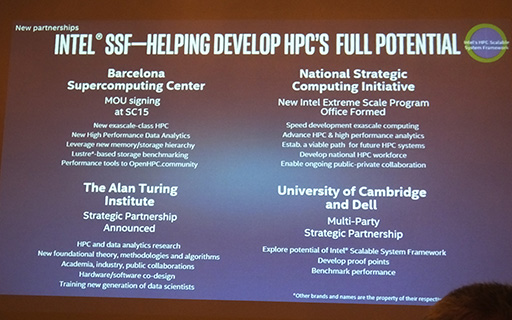

そのためにIntelが提唱したのが,すべてのHPC分野におけるニーズに応えられる統一されたプラットフォーム「Intel Scalable System Framework」(SSF)だ。

SSFは,XeonやXeon Phiなどのプロセッサによる「コンピュート」と「メモリおよびストレージ」,システム間を接続するインターコネクト技術の「ファブリック」,そして「ソフトウェア」の4つから構成されるプラットフォームである。これらは,Intelが2016年の市場投入に向けて開発中の次世代Xeon Phi「Knights Landing」(ナイツランディング,開発コードネーム)を想定したHPCシステムだ。

簡単にいえば,HPCシステムの販売業者は,Intelやパートナー企業が提供するSSF対応のコンポーネントやソフトウェアを組み合わせることで,HPCシステムを容易に構築できるようになるというわけだ。

|

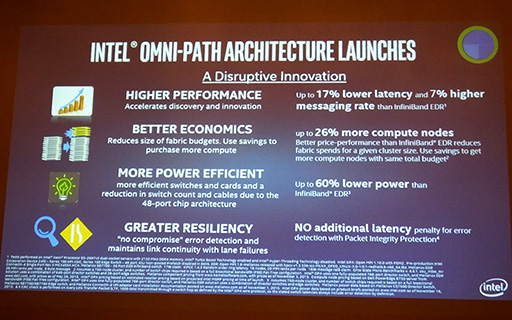

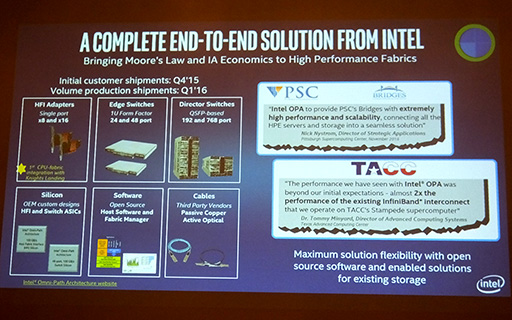

SSFでは,「Intel Omni-Path Architecture」(以下,Omni-Path)と呼ばれるファブリックインタフェースを利用して,プロセッサ間およびシステムボード間の接続を可能にしているのも特徴である。HPC分野では,システム同士の接続に「InfiniBand」というファブリックインタフェースが広く使われているが,Omni-Pathはこれの置き換えも狙っていると,Saleh氏は説明していた。Omni-Path用のスイッチや外部接続ケーブルシステムといったコンポーネントも,Intelがパートナー企業と協力して用意するそうだ。

|

|

|

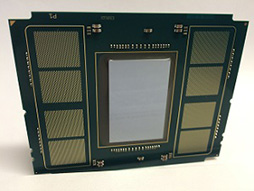

Silvermontアーキテクチャをベースに,HPC向けの「AVX-512」命令を拡張したCPUコアを72基集積したCPUで,プロセッサパッケージには,3D積層のDRAMを16GB搭載するという(関連記事)。

プロセッサパッケージ上のメモリ以外に,外部接続のメモリとしてDDR4 DRAMを使用できるほか,IntelとMicron Technologyが共同開発した「3D XPoint」(3Dクロスポイント)メモリを,DDR4 DRAM用のDIMMソケットに装着することで,大容量で高速な不揮発性メモリを搭載することも可能であるそうだ。

|

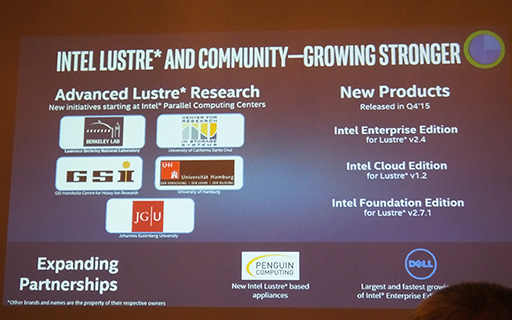

HPC向けのストレージシステムとしては,オープンソースのファイルシステム「Lustre」(ラスター)を使ったシステムが提供される。これは,多数のプロセッサが同時アクセスを行うHPCでの大容量データ運用を想定したストレージシステムで,ビッグデータ処理などに向いているという。Saleh氏によると,通常のストレージシステムでメモリへの読み込みに10分ほどかかっていた処理が,Lustreの導入で10秒に短縮された事例もあったそうだ。

|

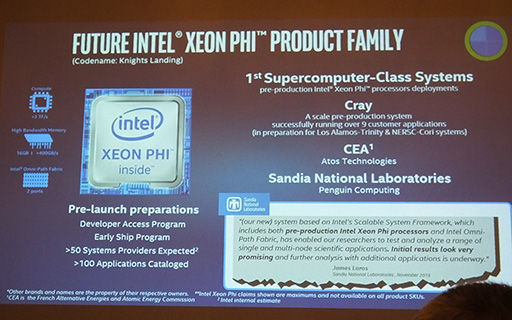

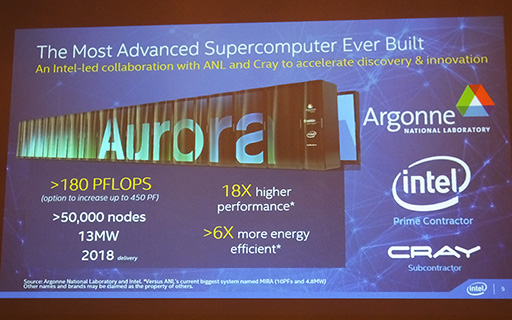

SSFを応用したHPCシステムの事例として,2015年4月に,IntelとスーパーコンピュータメーカーのCrayが米国エネルギー省から受注した次世代スーパーコンピュータ「Aurora」が挙げられた。このシステムでは,Knights Landingのさらに次世代となる「Knights Hill」(ナイツヒル,開発コードネーム)をベースにするのだという。

Knights Hillは,Knights Landingと互換性を持ち,10nmプロセスで製造される後継プロセッサで,当然ながらSSFに対応する。Saleh氏は,このAuroraで,

|

すでにいくつものメーカーがSSFを採用予定であるそうで,2016年第1四半期には,リファレンスデザインなどを含む「Intel SSF Design Guidance」が提供されるとSaleh氏は予告していた。

|

- 関連タイトル:

Xeon Phi

Xeon Phi - この記事のURL: