ニュース

これで分かるSkylakeマイクロアーキテクチャ。性能向上と省電力化のために加えられた多くの改良が明らかに

|

9月2日には,それに続く第2弾のデスクトップPC向け,およびノートPC向け計46製品が一斉に発表され,名実ともに「現行モデル」になったと述べていいだろう。

しかしこのSkylake,14nmプロセスで製造される新しいマイクロアーキテクチャということ以外,詳細な情報がなかなか公開されなかった。そのため,「テストしてみるとこれだけの性能向上が見られる」とはいえるものの,マイクロアーキテクチャの特徴に踏み込んでの解説というのは,難しい状況が続いていたものだ。

とはいえ,そうした状況も今ではだいぶ変わってきており,CPUコアやGPUコア,キャッシュメモリや周辺回路に加えられた,さまざまな改良点が明らかになってきている。そこで本稿では,Skylakeのマイクロアーキテクチャに加えられた改良点を,なるべく分かりやすく解説してみたいと思う。

なお,実際の性能検証は本稿の対象外となるので,性能に興味のある人は,すでに掲載済みのレビュー記事や基礎テストレポートを参照してほしい。

スケーラビリティに優れるSkylake

IntelはSkylakeが,以下に挙げる4つの点で特徴を持つとしている。本稿でも,この4点を軸にSkylakeの詳細を説明していきたい。

- スケーラビリティ

- 性能

- 消費電力

- グラフィックス

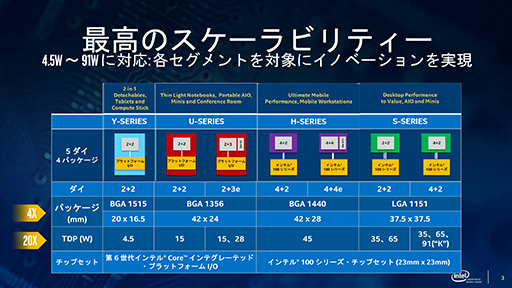

1.の「スケーラビリティ」(Scalability)とは,拡張性や柔軟性という意味の言葉で,ここでは,1つのマイクロアーキテクチャから,さまざまなバリエーションのCPU製品を作れる柔軟性がある,という意味だと理解しておけばいい。

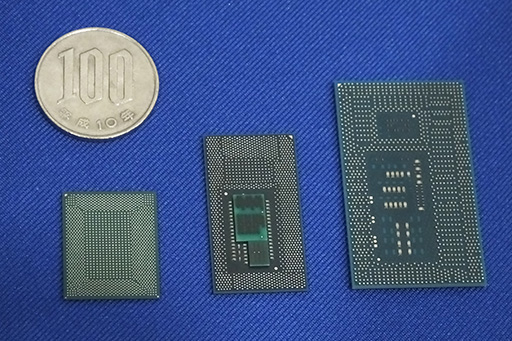

46製品がリリースされたときの記事でもお伝えしているとおり,Skylakeマイクロアーキテクチャに基づくCPUは,いまのところ,デスクトップPC向けの「Skylake-S」と,その派生モデルで倍率ロックフリーの「Skylake-K」,そして,ゲーマー向けなどの高性能ノートPC向けとなる「Skylake-H」,薄型ノートPC向けとなる「Skylake-U」,そしてタブレットや2-in-1向けとなる「Skylake-Y」といった具合で,対象となる市場ごとに,仕様の異なるさまざまな製品バリエーションがある。

|

|

付け加えると,Skylake-YとSkylake-Uでは,PCH(Platform Controller Hub,いわゆるサウスブリッジ)機能をまとめたSoC(System-on-a-Chip)的な構成も用意されている。これに“クロック違い”も加わることで,いきなり48製品(=2+46)というラインナップになっているわけである。

CPUコア側には「IPCを増やす工夫」がいくつも導入される

2.の「性能」は,さまざまな改良によって改善が図られているのだが,

Skylake世代のCPUコアでは,1クロックあたりに並列実行できる命令数(Instructions Per Clock,以下 IPC)を,前世代のBroadwellマイクロアーキテクチャよりも増やす工夫が盛り込まれている。

現在のx86アーキテクチャでは,IPCの向上がそろそろ限界に近づいており,細かく工夫したからといって,どんな場合でもIPCを大きくできるわけではない。それでも改良されたマイクロアーキテクチャに合わせてソフトウェアを最適化することで,CPUコアの性能を最大限に引き出すことは可能だ。

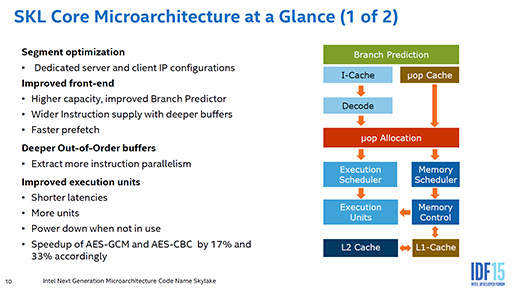

というわけで具体的な改良点だが,1つめは,x86/x64命令をCPUコア内部で実際に処理するマイクロ命令(μOPS)に変換するデコーダの拡張である。

x86/x64命令には,「単純な命令」と「複雑な命令」という2種類の区分けがあり,Skylakeでは,単純な命令用のデコーダが4基,単純な命令と複雑な命令のどちらにも対応した兼用デコーダが1基で,合計5基が搭載されている。BroadwellやHaswellの世代では,順に3基,1基だったので,単純な命令用のデコーダが1基増えているわけだ。

|

なお,この5基が同時に命令をデコードできれば理想的なのだが,どんな場合でも同時にデコードできるわけではない。デコーダに送られる5つの命令が,すべて単純な命令の場合や,複雑な命令が1つだけ含まれる場合には,5命令の同時デコードが可能となる一方,複雑な命令が2つ以上あると,そこでデコードはいったん中断されてしまい,残りは次のクロックでデコードされることになる。

ソフトウェアの最適化によって,5命令同時デコードの可能性を高めることはできるので,「Broadwell&Haswell世代では最大4命令同時デコードを行える可能性があったのに対し,Skylakeでは最大5命令の同時デコードを行える可能性が生まれた」くらいの理解が妥当ではなかろうか。

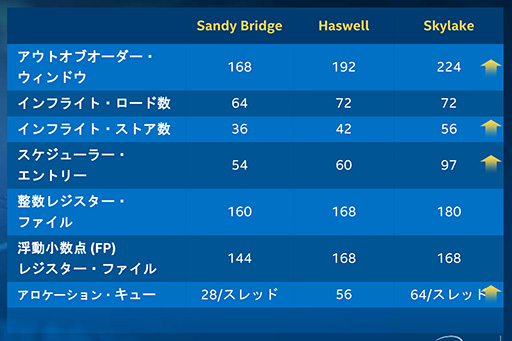

IPCを増やす改良点の2つめは,5命令同時デコードの対応に合わせて,μOPSを実行する処理機構の内部を強化したこと。たとえば,アウトオブオーダー実行を行う命令数は,Haswell/Broadwell世代の192命令から224命令に,μOPSの実行スケジューラが管理する命令数は,同60から97へと拡張されているといった具合だ。

そのあたりをまとめたものが下のスライドだが,これを見ると,スケジューラ(※下のスライドでいう「スケジューラー・エントリー」)やストアバッファ(※同「インフライト・ストア数」)が拡張されているのも見て取れよう。

|

命令には依存関係があり,他の命令が実行された後でなければ実行できないこともありうる。また,同種の演算は同じ実行ユニットを使うので,使いたい実行ユニットに空きがなければ,どれかの実行が終わるまで待たねばならない。よって,デコーダ部分の制約だけでなく,実行ユニットの数や使用状況によっても,実際のIPCは変わってしまうことになる。

ただそれでも,デコーダと実行ユニット,バッファなどが拡張された以上,ソフトウェア全体で見れば,Skylakeの平均IPCは,BroadwellおよびHaswell世代より高くなると期待できるわけだ。

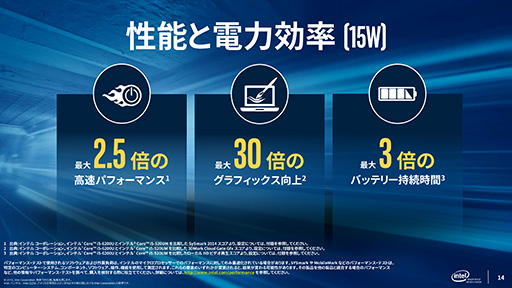

Intelは,Skylakeの具体的な性能として,同社が第1世代Coreプロセッサとする「Nehalem」――Coreの名を冠した製品はそれ以前にもあったが,Intelの扱い上はNehalemが初代となっている――世代と比較して,最大で2.5倍のCPU性能向上を実現できたとしている。この根拠は,Nehalem世代の2コア4スレッドCPUで,TDP 18W,定格動作クロック1.067GHz,最大動作クロック1.867GHzの「Core i5-520UM」と,Skylake世代の2コア4スレッドCPUで,TDP 15W,定格動作クロック2.3GHz,最大動作クロック2.8GHzの「Core i5-6200U」をテストで比較した結果とのことだ。

同程度のTDPで比較したとき,定格動作クロックが2倍以上,最大動作クロックが約1.5倍に達し,パイプラインも強化されていることを考えると,合わせて性能差が最大2.5倍あるというのは,おおむね納得の範囲といえるだろう。

|

そのほかアーキテクチャ面における強化点としては,セキュリティにかかわる新機能「Software Guard eXtensions」(以下,SGX)と「Memory Protection eXtension」(以下,MPX)の導入が挙げられる。

SGXは,命令実行フローやメモリを保護する状態を作り出す新命令で,高い優先度で動くマルウェアによる攻撃からも,実行中のプログラムを保護できるようになるというものだ。

一方のMPXは,プログラムがそれ自体の管理外にあるメモリにアクセスできないよう,事前にチェックする機構。マルウェアなどでは,それ自体の管理するメモリと隣接する管理外のメモリにアクセスすることで,不正な操作を行う手法が多く使われているが,MPXを使うことで,こうしたアクセスを禁止できるようになる。

多くの改良が盛り込まれたSkylakeの省電力技術

3.の消費電力は,Skylake世代に導入された電力管理関連の強化を意味する。これにはいくつかの要素があるので,順に説明していこう。

Broadwell/Haswell世代と比べて,ハードウェア面で大きく変わったのが,CPUに対してさまざまな電圧を供給する「電圧レギュレータ」(Voltage Regulator,以下 VR)の構成だ。

Broadwell/Haswell世代では,VRをCPUパッケージ内に搭載した「Fully In

|

FIVRには,いくつかのメリットとデメリットがあるのだが,最大のデメリットとしては,CPUに内蔵されることで発熱が大きくなり,周波数向上に対する制約になることが挙げられる。逆にいえばSkylakeは,VRを外付けにしたことで,動作クロックを上げやすい構造になった。

また,FIVRは,電力効率や応答速度などの点では外付けよりも有利である一方,発生するノイズの量が多く,CPUコアのすぐ側へ配置するためには,追加のノイズ対策が必要というデメリットもあった。そういう理由からIntelはSkylakeでFIVRを諦めた,ということのようである。

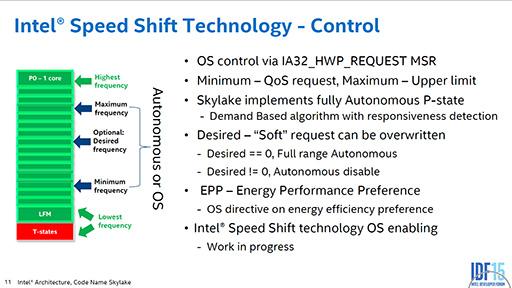

電力管理面における2つめの大きな変化は,「Intel Speed Shift Technology」(以下,Speed Shift)の導入である。

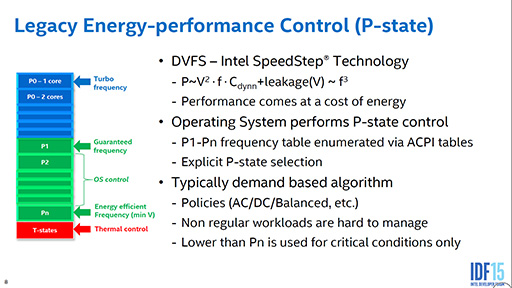

大雑把にいうと,Speed Shiftは,従来の「Enhanced Intel SpeedStep Technolgoy」(以下,EIST)および「Intel Turbo Boost Technology」(以下,Turbo Boost)の代わりに,CPUコアの動作クロックと駆動電圧を広い範囲で自動調整するというものである。

従来のEISTでは,CPUの定格動作クロック(Guarantied Frequency。「P1」ステートともいう)を上限,設定された最低動作クロックを下限とした範囲で,OSがクロック周波数や動作電圧を切り替えて制御していた。CPU負荷が低くなったことをOSが検知すると,動作クロックを下げて,逆に負荷が高くなったことを検知すると,クロックを上げる実装だ。

そしてTurbo Boostは,CPUの動作温度などをチェックして,余裕がある場合には,P1よりもクロックの高い「P0」状態へ移行させる機能だった。Turbo Boostを使うと,負荷の高い処理をより短時間で終了させ,残りの時間をアイドル状態へ移行できることから,処理時間の短縮と最終的な消費電力の低減を両立できる,というわけである。

|

これに対してSpeed Shiftでは,「Lowest Frequency Mode」(以下 LFM)というステートと,マルチコアCPUのうち,1コアの達する最大動作クロックのステート「P0-1Core」までを「当該CPUにおけるクロックの変動範囲」として,PCメーカーが,この範囲で任意に「最大動作クロック」「最小動作クロック」を設定できる。一般に,前者は筐体の冷却能力,後者はサービスの品質を維持できる最低ラインで設定されることになるだろう。

プロセッサごとに,P1ステートの動作クロックであるGuarantied Frequencyと,低消費電力での動作に最適化されたクロックで,Intelが「Pe」と呼ぶ「Most efficient frequency」は設定されるが,PCメーカーは,それを利用してもしなくてもいい。

|

さらにSpeed Shiftでは,PCメーカーが設定した範囲の中で,負荷状況に応じ,そのときどきで最も電力効率の高い動作クロックと電源電圧の組み合わせをCPU側で自動設定できる機能も用意されている。EIST+Turbo BoostではOS側で制御されていたのに対し,Speed ShiftではCPU側で主体的な自動制御を行えるようになったのだ。

とはいっても,OS側から「処理優先するのか,消費電力削減を優先するのか」といった条件付けは行えるので,まったく介入できないわけではない。

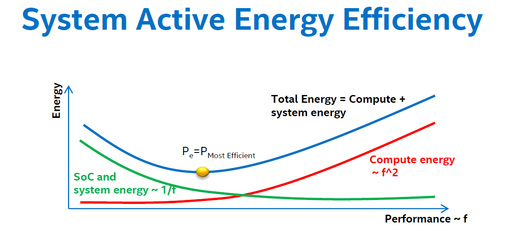

CPU側におけるクロックの自動調整は,システム全体の消費電力とCPUの消費電力を勘案して行われる。システム全体の消費電力は,処理時間が短くてアイドル時間が長くなるほど小さくなり,CPUの消費電力は,クロック周波数の2乗に比例して大きくなる。この両方を合わせた全体の性能対消費電力比をグラフ化すると,凹型(皿型)になるので,その最も低いところを探して,実際の動作クロックを設定する仕掛けだ。

|

もちろん,単純に処理の負荷だけを見て動作クロックを変えようとしても,うまくいかない。たとえば,CPUとiGPUが並列して動作しているとき,どちらか一方だけが先に処理を終えても,もう一方が動いていれば,CPU全体をアイドル状態に入れることはできないため,電力効率が悪くなってしまう(※後述するが,機能ブロックごとの電力制御は別の話)。

その点Speed Shiftは,どのプロセッサコアが動作しているのかといった状態も検出し,クロックを上げるかどうかを決定できるようになっている。付け加えるなら,動作クロックを上げなくても短時間で終了する処理や,そうした処理が一定間隔で繰り返されるようなケースでは,いたずらに動作クロックを上げて消費電力の増大を招くことが生じないような工夫も盛り込まれている。

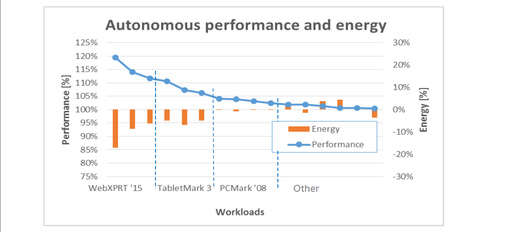

下に示したグラフのスライドは,Speed Shiftによる自動クロック調整と,従来のEIST+Turbo Boostを使った場合とで,消費電力と処理性能を比較した結果とされるものだ。オレンジの棒グラフが「削減した消費電力の割合」,青い折れ線グラフが「向上した処理性能の割合」を示す。横軸に並んでいるのは,評価に使われたベンチマークプログラムで,左から,Speed Shiftの効果が高かった順に並んでいる。

一部のソフトウェアで,自動調整が消費電力の増大を招いているケースはあるが,この評価の範囲において,性能が下回ることはない。少なくとも,EIST+Turbo Boostと同等の処理性能は確保されているようだ。

|

さて,省電力化に役立ちそうな機能であるSpeed Shiftだが,利用にはOS側の対応が必要で,しかも,現時点で対応済みのOSは存在しないという問題がある。OS側で対応しない場合はEIST+Turbo Boostで動作するので,Skylakeで自動的な動作クロック制御を利用できないわけではないのだが,もったいない話なのも確かだ。

現在,MicrosoftとIntelは共同で,WindowsのSpeed Shift対応を進めている最中とのことだが,おそらくは,最新のWindowsであるWindows 10からの対応が優先されることになるのだろう。従来のOSがサポートされるかどうかは,今のところなんともいえない。

話を戻そう。

Skylakeの電力管理における3つめの変化は,CPUを構成するユニットごとの電力制御が,よりきめ細かく行われるようになったことだ。「実行中であっても,不要な部分の電源はカットして,電力を削減する」機能自体はこれまでのCoreプロセッサにも実装されていたが,Skylake世代においては,電源オン/オフの対象となるユニットを見直し,より細かい単位で制御できるようになった。これまではユニットの一部だけを使う場合でもユニット全体の電源をオンにする必要があったのに対し,Skylakeでは,当該ユニット内で電源をオフにできる部分を増やした,といったイメージだ。

もう少し具体的に話をすると,Skylakeではまず,CPUコア,リングバス,iGPU内の実行モジュール(スライス)やiGPUのロジック部分,I/Oやメモリコントローラなどのシステムエージェントといった4つのユニットに対して,独立した電源制御を行えるようになっている。eDRAMを搭載する製品では,eDRAMのインタフェース(eDRAM I/O)も電源制御の対象だ。

|

そのうえで,各ユニットをさらに細かく分割して管理し,「分割して管理される単位」ごとに電源のオン/オフができるようになっている。

たとえば,CPUコア内部にあるAVX2命令の実行ユニットは,AVX命令やAVX2命令を実行しないときにはオフになる。AVX命令セットは,Sandy Bridgeで導入されたものであり,それ以前に作られたプログラムだと,基本的には使われないはずだ。であれば,不要なときは,

そのほかにも,製造プロセスや回路設計などの工夫により,回路の動的な静電容量――電源がオンになったとき,回路が持つ静電容量に電力が蓄積されるが,これは回路の動作自体に必要なものではないため,回路の電源がオフになったとき漏れてしまう無駄な電力だ――を削減し,電源がオンになったときに消費される電力を削減するといった工夫も凝らされている。

電源管理における4つめの変更は,「シナリオベースの電力制御」だ。

たとえばビデオ再生時の処理は,ストレージやネットワークからビデオデータを読み込む処理と,データ形式に従ってデコードする処理,そして表示処理に大きく分かれるが,Skylake世代では,こうした特定の処理を考慮して,処理単位で適切な電力管理を行えるようになったのである。

|

前段でも軽く触れたとおり,Skylakeで,Nehalemと比べて最大3倍のバッテリー駆動時間を実現したというのがIntelの主張だが,これは,まさにいま紹介した,「ビデオ再生というシナリオ」に沿った場合の話となる。

なお,Skylakeでは,CPUコアの休止状態の1つである「C1」ステートの消費電力も,前世代と比べて削減されているとのことだ。

大きく強化されたiGPU

4K解像度の60Hz出力も可能に

4.のグラフィックスは,もちろんiGPUの話だ。

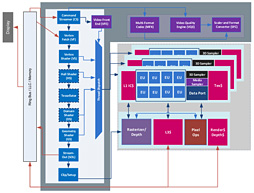

Intel製のiGPUは,チップセットに内蔵されていた「Intel Graphics Media Accelerator」(Intel GMA)の頃から代を重ねて,Skylakeで9世代めとなることから,「Processor Graphics Gen9」(以下,Gen9)と呼ばれることもあるが,そのブランド名は,HD Graphics 500シリーズ,もしくはIris Graphics 500シリーズとなる。いずれも,Intel製iGPUとして初のDirectX 12対応だ。

先述したとおり,Skylakeでは電力効率が非常に重視されているわけだが,iGPUでも,内部構成が見直され,消費電力あたりの性能が向上しているという。また,メディア再生時のデコード処理を行うハードウェアを強化し,多くの処理をiGPU側のハードウェアで行うようにしたことで,CPUコアをアイドル状態に保つことができるようになり,結果,ビデオ再生時には1W以下,ビデオ会議の場合でも1W程度の消費電力を実現できているとのことだ。

先述したシナリオベースの電力制御は,Gen9に統合されるハードウェアのメディア機能を使うことで実現されるわけである。

|

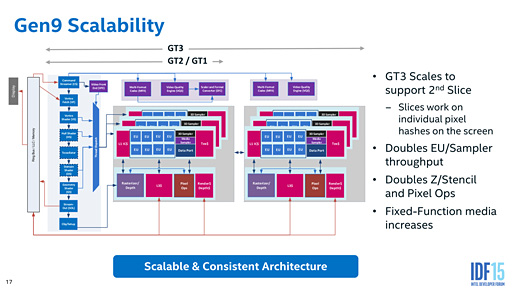

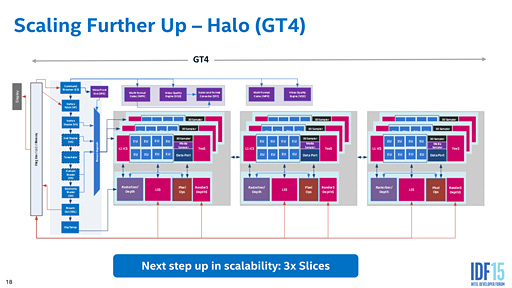

1つのSliceは,シェーダ演算などを行う実行ユニット(Execution Unit,EU)が8基と,L1・L2キャッシュ,ローカルの命令発行ユニットなどからなる「Subslice」(サブスライス)が3基と,L3データキャッシュ,ラスタライザなどで構成される。よって,SliceあたりのEU数は24基だ。そして,Sliceの数は目標となる性能および消費電力によってスライス数は柔軟に変更できるようになっており,GT1とGT2は1つ,GT3は2つ,最上位のGT4は3つになる。GT4の場合,EU数は72基(8×3×3)となる計算だ。

|

|

Sliceあたり24基のEU(8 EU×3 Subslice)という基本構成は,

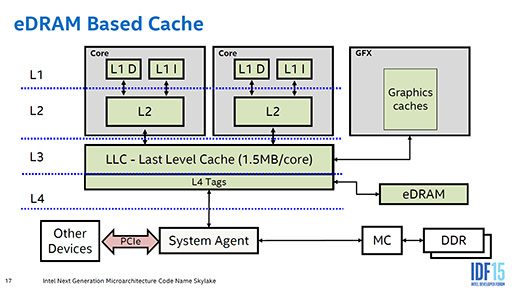

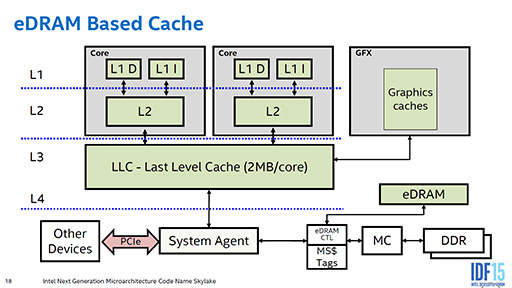

ところで,本稿の冒頭で,iGPUにはeDRAMを組み合わせたものがあるという話をしたが,具体的には,GT3とGT4にのみ,eDRAMを組み合わせた「GT3e」「GT4e」が用意される。そして,これらGT3e&GT4eのeDRAMは,BroadwellおよびHaswell世代のeDRAMから変更が入っている。

BroadwellおよびHaswellの場合,eDRAMはソフトウェアから制御可能な「LLCの外側にあるキャッシュメモリ」として動作しており,eDRAMにキャッシュされた領域がメインメモリアドレスのどこになるのかを記録した「タグ情報」は,LLC内に保存されていた。

|

しかし,SkylakeのiGPUでeDRAMは,ソフトウェアから制御できないキャッシュとして動作する。合わせてLLCは,eDRAMのタグ情報を持たない,純粋なキャッシュメモリとして機能するようになっている。

eDRAMのタグ情報は,System Agent(システムエージェント)内にあるeDRAMコントローラへ保存され,その結果,eDRAMは,メインメモリと並列の「高速メモリ」として動作するようになった。eDRAMはメモリコントローラの直前にあるため,メインメモリと同一の内容を保持できる仕組みだ。

ある意味,Gen9とGen8のiGPUで一番大きく変わったのは,このeDRAMの扱いかもしれない。

|

繰り返すが,eDRAMはソフトウェアから制御できない。そのためここには,ソフトウェアから「キャッシュしない」と指定した領域のデータも含まれることになる。そのため,たとえばグラフィックスドライバが,「CPUからアクセスする必要のないグラフィックス関連データのあるメモリ範囲」をLLCでキャッシュしないよう指定しておけば,LLCをムダに占有することがなくなるため,CPUがLLCを有効活用できるようになる。同時に,グラフィックス関連の処理では,eDRAMにキャッシュされたデータへ高速にアクセスできるという,キャッシュの使い分けが可能になる。

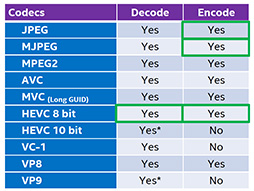

なお,先ほど「ビデオデコードやエンコード用の固定機能」としてさらっと流したところにも拡張は入っており,Gen9 Graphicsでは,メディア処理用の「Multi-Format Codec」(以下,MFX)および「Video Quality Engine」(以下,VQE),「Scaler and Format

|

VQEは,ビデオデータを処理する機能で,ノイズフィルタリング処理などを行う。Gen9 Graphicsでは,Webカメラからのビデオ処理用として,ホワイトバランスやガンマ修正,カラー変換,RAW現像用のDeBayerフィルタリング処理などを行えるようになっている。

SFCは,解像度やフォーマットを変換する機能で,Gen9 Graphicsにおける完全新設だ。

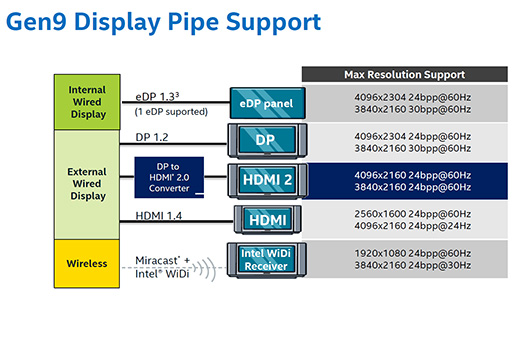

また,Gen9 Graphicsではディスプレイコントローラ部分も強化されており,DisplayPort 1.2やembedded DisplayPort(以下,eDP) 1.3を使った場合,4096×2304ドット/24bitピクセルの60Hz出力表示が可能になった。さらに,DisplayPort to HDMI 2.0コンバータを経由すれば,4096×2160ドット/24bitピクセルの60Hz出力をHDMIでも行える。Skylake世代のPCでは,4K@60Hz表示が当たり前のものとしてできるようになるだろう。

|

Skylakeのマイクロアーキテクチャにおける主な特徴は,以上のとおりとなる。

Skylakeは,製品の発表や詳細な技術説明が行われるよりも先に最初の製品が発売され,技術説明や正式なラインナップ発表はその後という,Intel製CPUとしては異例ともいえる形で登場することとなった。異例づくめの背景には,

もちろん,現在のWindowsでもSkylakeの性能を発揮できないわけではないのだが,消費電力面での利点をフルに発揮するには,Windows 10のSpeed Shift対応を待つ必要がありそうだ。その意味では,急いでSkylakeや搭載PCを買わずに,対応が済んでから買うという判断も間違いではないだろう。

- 関連タイトル:

Core i7・i5・i3・M(Skylake)

Core i7・i5・i3・M(Skylake) - この記事のURL: