ニュース

Intel,基幹サーバー向けのCPU新製品「Xeon E7 v3」発表。マルチスレッドの特定処理を高速化する新命令「TSX」はゲーマー要注目かも

|

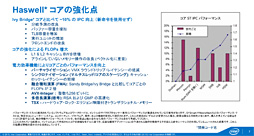

開発コードネーム「Haswell-EX」として知られてきたXeon E7 v3は,Ivy Bridge-EXベースの現行製品「Xeon E7 v2」を置き換えるプロセッサとなる。

最大で18コア36スレッド対応となり,しかも1システムあたり最大8ソケット構成が可能と,ゲーマーが手を出すようなCPUではまったくないのだが,実装された機能のなかには,将来,PC向けプロセッサから利用できるようになりそうなものもあったりするので,今回はXeon E7 v3の概要を簡単にまとめてみることにしよう。

4-way対応のデータセンター向けXeonが

ついにHaswellマイクロアーキテクチャを採用

発表時点におけるXeon E7 v3のラインナップは12製品。サーバー向けが表1のとおり8製品,HPC(High Performance Computing)などの特定用途向けが表2のとおり4製品となる。

Xeon E7 v2では最大2ソケットに対応するE7-2000番台がラインアップに用意されていたが,表のようにXeon E7 v3ではE7-2000番台が消え,4ソケット以上に対応するラインナップとなった。小規模サーバー向けの2ソケット対応モデルとしては2014年9月に発表済みの「Xeon E5 v3」があるので,それと棲み分けることになったのだろう。

なお,Xeon E7 v3は,全製品が自動クロックアップ機能「Intel Turbo Boost Technology 2.0」に対応するが,原稿執筆時点で最大動作クロックは明らかになっていない。

|

|

|

ただ,Xeon E5 v3ファミリーとまったく同じというわけでもない。最大のトピックは新命令「TSX」だが,これについては後述するとして,CPU内部でリングバスの構成が変更されたのも,大きなポイントとなるだろう。

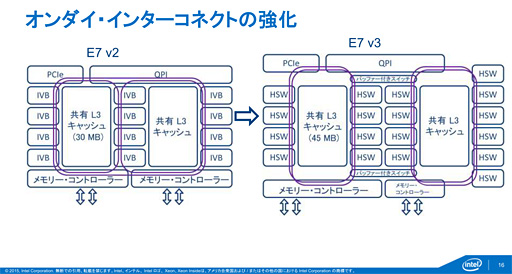

具体的には下に示したスライドのとおりで,10コア以上のXeon E7 v3では,内部が2つのブロックに分かれ,ブロックごとに内部が完全に二重化されたリングバスで結ばれ,各ブロックのリングバスは,2基のバッファ付きスイッチを介して接続する形になったのだ。つまり,10コア以上の製品はバッファ付きスイッチを介した,デュアルコアCPU的な“デュアルブロック”構造になっているのである。

Xeon E7 v2でも10コア以上の製品だとブロック自体は2つに分かれていたが,リングバスは,ブロック間をつなぐものと,ブロック内部とで,非対称な二重リングバスになっており,コア間の接続に対称性がなかった。Xeon E7 v3では,そこが改善されたことになる。

|

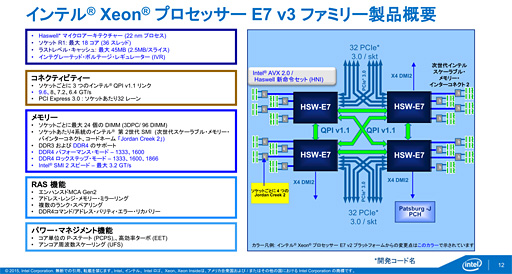

4ソケット版を例に,Xeon E7 v3プラットフォームの概要を示したのが下のスライドだ。大まかな構成はXeon E7 v2と変わっていないが,はっきりした青色(=水色でも濁った青でもない青)の文字および矢印で書かれているのがXeon E7 v3における新要素となる。

まず,プロセッサ間をつなぐQuick Path Interconnect(QPI)は,Xeon E7 v2と同じくバージョン1.1ながら,動作クロックの引き上げにより,従来の最大8GT/sを超える最大9GT/sがサポートされた。これによりマルチプロセッサの性能が向上しているという。

|

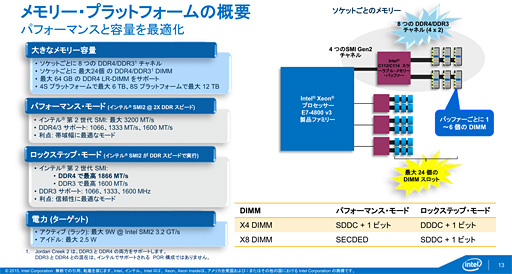

DDR4メモリのサポートが追加されたのも,Xeon E7 v3における大きな特徴の1つだ。というか,DDR4/DDR3両対応となったのが,最大の特徴と言っていいかもしれない。

「Scalable Memory Interconnect」(以下,SMI)と呼ばれるブリッジを介して接続され,プロセッサあたり4本のSMIチャンネルを持つのはXeon E7 v2と同じだが,Xeon E7 v3ではSMIが第2世代へ移行しており,チャネルあたりの帯域幅が従来の1.6GT/sから最大3.2GT/sへと倍増を果たした。端的に言えば,SMIがDDR3メモリ比で2倍の帯域幅を持つDDR4メモリに対応したのに合わせ,SMIチャネルの帯域幅も2倍にしたといった感じだ。Intelによれば,最大18コアという多数のコアが集積されたCPUにとって重要な足回りにあたるメモリ性能が,かなり改善されることになるとのことである。

1基のSMIは最大6枚のDIMMを搭載でき,プロセッサあたり最大24 DIMMの構成が可能。8ソケットシステムでは最大192 DIMMで12TBもの容量を実現可能だ。このあたりはXeon E7 v2から変わっていないが,基幹サーバー向けにふさわしい仕様とはいえるだろう。

|

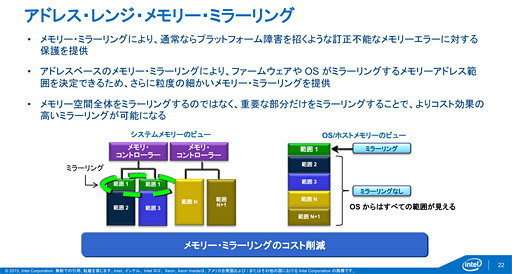

Xeon E7 v3ならではの新命令となるTSX

Xeon E7 v3では,いわゆる「ファイブナイン」,年間稼働率99.999%を実現するために用意される「Run Sure Technology」周りに多くのアップデートが入っている。たとえば,2枚のDIMMを使ってミラーリングする技術として従来製品でも採用されている「Memory Mirroring」(メモリミラーリング)に加えて,Rank(ランク)ごとにスペアモジュールを設定してメモリのリカバリを行う「Rank Sparing」(ランクスペアリング)や重要なメモリ領域だけミラーリングする「Address Range Mirroring」(アドレスレンジミラーリング)が新たに追加されている,といった具合だ。

|

このような,いわゆるRAS――Reliability(信頼性)とAvailability(可用性),Serviceability(保守性)頭文字を取った専門用語――機能はPCユーザーには大げさすぎる話になるが,ここで出てくるのが,先ほど後述するとしたTSXだ。

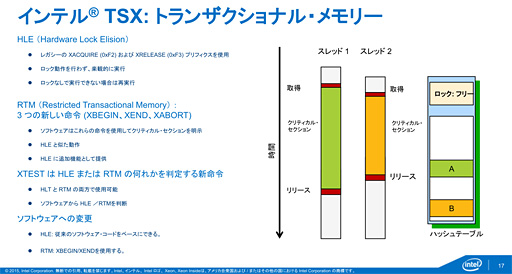

TSXは「Transactional Memory」(トランザクショナルメモリ)から付けられた造語で,Xeon E7 v3が初めての採用例となる。

マルチスレッドやマルチプロセスのOSでは,複数のスレッド(やプロセス)が,あるメモリ上のデータの書き換えや参照を行うコードを同時に実行することが起こりうるが,そのとき,不都合の生じる場合がある。

そこで,あるメモリ上のデータに対して書き換えや参照を行うコードを実行するスレッドは1つに制限し不都合が起きないようにするのが一般的だ。コードの手前に「遮断機」を入れて車を1台ずつしか通せなくするイメージで,1つのスレッドしか実行できないよう制限されたコード部分は「Critical Section」(クリティカルセクション)と呼ばれる。

このクリティカルセクションは,マルチプロセッサシステムにおいて厄介な存在だ。あるCPUがクリティカルセクションを実行しているとき,同じクリティカルセクションを実行する他のCPUコアは「待ち状態」に入れて止めなければならず,CPUコアを効率的に使えなくなってしまう。

TSXは,そんなクリティカルセクションにハードウェアで対応しようとする命令セットだ。具体的には,とりあえずクリティカルセクションを実行してしまいつつ,他のスレッドとの衝突をCPU側で検出し,衝突が起きたら実行結果を破棄してクリティカルセクションを再実行する動作になるという。CPUがスレッドの衝突を検出してくれるため,調停のオーバーヘッドを削減でき,さらに,クリティカルセクションにともなって生じる「Deadlock」(デッドロック)――いくつかの要因が絡んで,待ち状態から永遠に抜けられなくなってしまう現象――も解決しやすくなると思われる。

|

Intelによれば,このTSXを使ってインメモリデータベース「SAP HANA」をXeon E7 v3に最適化したところ,Xeon E7 v2比で5.9倍もの性能が得られたそうだ(※この5.9倍というのは原稿執筆時点の数値で,今後,最適化が進むと,アップデートされる可能性があるともされている)。

|

また,ゲームのようなアプリケーションも最近はすべてマルチスレッドで設計されているため,そこにはクリティカルセクションが必ず存在する。つまりTSXがあればゲームでさえ性能の向上が期待できるわけだ。

TSXはXeon E7 v3で初めて採用された機能だが,サーバー用途に限らない効果が期待できる以上,将来的には,PC向けのCPUにも“下りて”くる可能性があるだろう。

Xeon E7シリーズはRAS機能が目玉になっているので,全般的にはPC向けCPUと少し距離がある存在になっているが,こうした汎用性のある先進機能がさりげなく実装されたりするので目が離せない。今後もIntelの製品を幅広くチェックしておくと,将来へのヒントがつかめる可能性があるので,新情報があればまたお伝えしたいと思う。

- 関連タイトル:

Xeon

Xeon - この記事のURL: