ニュース

AMD,次期APU「Carrizo」の詳細情報を公開。Kaveriと同じ28nmプロセス技術を採用しながらトランジスタ数を29%増量できた秘密とは

|

2014年10月に発表されて以来,なかなか詳細が明らかにされることのなかったCarrizoだが,今回の発表でとくに製造技術に関わる情報が多く明らかにされたことで,その実像がだいぶ見えてきたといえよう。

本稿では,AMDが報道関係者向けに行った事前説明の情報をもとに,公表されたCarrizoの概要をレポートしたい。

Kaveriと同じ28nmプロセスを使いながら,

高密度化と電力性能を向上

Carrizoの概要は発表時のレポート記事に書かれたとおりだが,簡単におさらいしておこう。

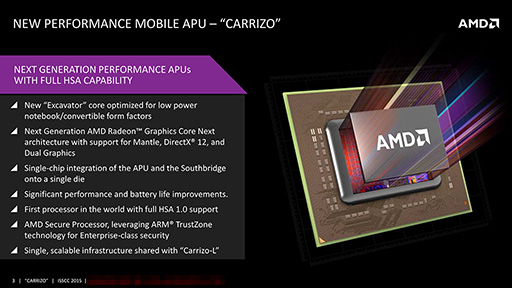

Carrizoとは,現行のAPUである「Kaveri」の後継となる製品で,CPUコアにはSteamroller系CPUコアの改良版である「Excavator」(エクスカベータ,開発コードネーム)を,GPUコアにはHSA 1.0(HSA:Heterogeneous System Architecture)に対応した「Graphics Core Next」アーキテクチャのGPUを採用する。さらに,今まではチップセットとして提供されていたサウスブリッジの機能が,CPUやGPUと同じダイ(半導体そのもの)に統合されたSoC(System-on-a-Chip)製品となるとのことだ。

また,CPUコアに「Puma+」,GPUコアにはHSA 1.0非対応のGPUを組み合わせた省電力版APU「Carrizo-L」も予定されている。ただ,今回の発表内容は,

|

さて,ここまでは既報の話で,ここからが今日の本題である。

CarrizoはKaveriと同じ28nmプロセスで製造されるのだが,Kaveri世代にはなかったサウスブリッジ機能がダイ上で統合されるので,そのまま統合するとダイサイズが増えすぎて歩留まりが悪化してしまう。そのうえAMDは,Carrizoの消費電力を低減させることも目指していたので,ダイサイズの増大は避けなくてはならない。

そのために,Carrizoでは集積度を大幅に向上させてダイサイズを縮小するために,とくにCPUコア部分の設計を刷新することにした。そこでAMDが採用した手段が,半導体プロセスを変更することだ。

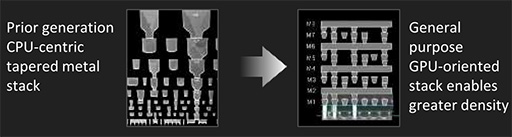

高性能を目指すPC用CPUとその他の半導体(たとえばスマートフォン向けSoC)では,半導体の各層で使われる配線の太さが異なるのが一般的である。CPUでは高性能化のために大きな電力供給が必要とされるので,細い配線の上に太い配線を重ねるプロセスが用いられており,これはAMDのAPUでも同様だった。

しかし,このような実装方法だと,どうしても半導体の中に無駄ができてしまうので,実装密度が低下してしまう。そのためPC用CPU以外の半導体では,内部で配線の太さを極端に変えるようなことは行われていない。そのほうがコンパクトなものを作れるからだ。

|

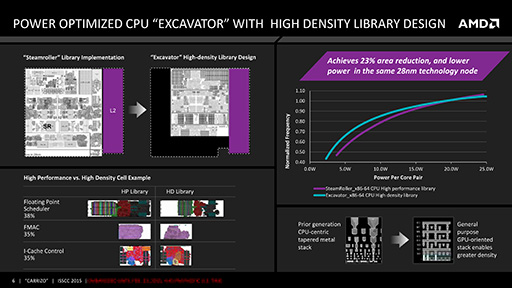

そこでCarrizoのExcavatorコアでは,「High-density Library」(高密度ライブラリ)デザインと呼ばれる一般的な半導体に近いプロセスに切り替えられた。このHigh-density Libraryを採用したことと,回路設計の最適化によって,Excavatorコアは前世代のSteamrollerコアと比べて,面積比で23%の縮小が可能になったという。

下に掲載したスライドは,左上にSteamrollerコアとExcavatorコアの全体を,左下に両CPUコアが備える機能ブロックごとの面積を比較した図が掲載されている。これを見ただけでも,Excavatorコアが大幅に削減されていることがうかがえるだろう。

|

GPUに適したプロセスで,APU全体の処理性能を底上げするCarrizo

さて,一般的な半導体向けのHigh-density Libraryを使うということは,Carrizoは高性能を重視するCPUには適さないプロセスで作られているということになる。だが一方で,コア数が性能を決めるGPUにはHigh-density Libraryのほうが適しており,Carrizoはこの特徴を生かしたプロセッサとなっているという。

AMDコーポレート・フェローのSam Naffziger氏は,Carrizoでプロセスを変更した2つの理由を説明した。1つは「CPUとGPUという,普通なら2つの会社に分かれているような設計チームがAMDでは社内にあるため,(両チームが)緊密に協力できた」ことだそうだが,もうひとつは「ベンチマークテストをはじめとするアプリケーションで,従来以上にGPUが活用される局面が増えている」からだという。

つまり,High-density Libraryの採用によってGPUコア数を増やすことができれば,

CPU向けプロセスからHigh-density Libraryにプロセスを切り替えたことで,

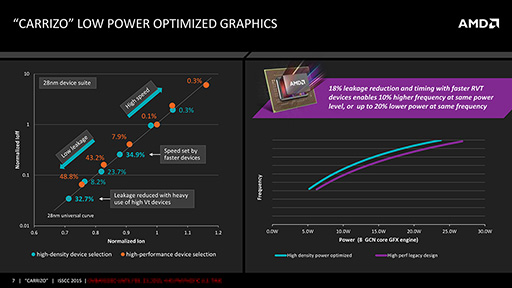

下に掲載したスライドの右側にあるグラフは,従来型プロセスとHigh-density Libraryで8基のGCN世代GPUコアを作った場合の,消費電力と動作クロックの変化を示したものだ。High-density Libraryのほうが,同じ動作クロックでも消費電力が低いことが読み取れるだろう。

|

ちなみに,左側のグラフは,GPUの漏れ電流をグラフ化したもので,赤丸がSteamrollerまでのプロセス,青丸がCarrizoのHigh-density Libraryでの漏れ電流を示しているらしい。らしいというのは,縦軸と横軸の単位や丸の横に書かれた数値の意味が説明されていないので,グラフが何を可視化したものかいまひとつ分からないのだ。青丸のほうがグラフの左下よりに描かれていることで,Carrizoは既存のプロセスよりも漏れ電流が少ない,ということを説明しているようだが。

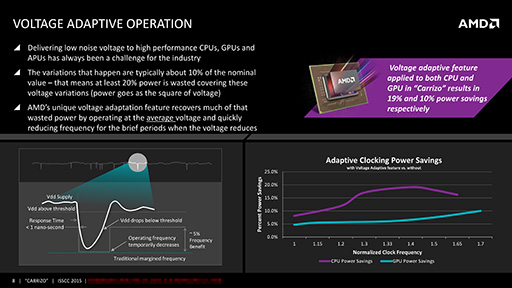

話を戻そう。半導体の高密度化が進むと,各部分への電圧供給がよりシビアになってくるという問題もある。そこでAMDは,Carrizoに新しい「Voltage Ad

Carrizoの電圧適応機能では,電圧の変動に要する時間を短くするとともに,無駄になる電力を大幅に抑えることを可能にしているという。下のスライド右側に示されているように,CPUでは最大19%,GPUでも最大10%の消費電力を低減したとAMDではアピールしている。

|

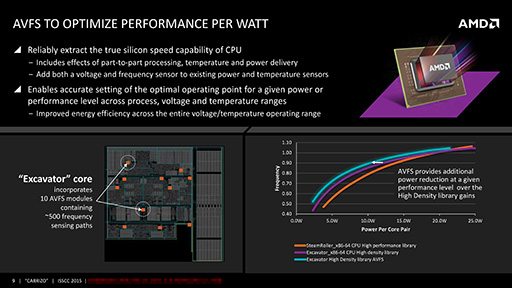

性能向上と消費電力低減のために,CPUコア内のセンサーも強化されている。Excavatorでは「Adaptive Voltage and Frequency Scaling」(以下,AVFS)と呼ばれるセンサーモジュールが10個埋め込まれており,温度や動作クロック,電圧を監視しているという。このAVFSが得たデータをもとに,CPUの動作を適切な状態に維持することで,CPUの性能を最大に引き出して電力効率を向上させているそうだ。

|

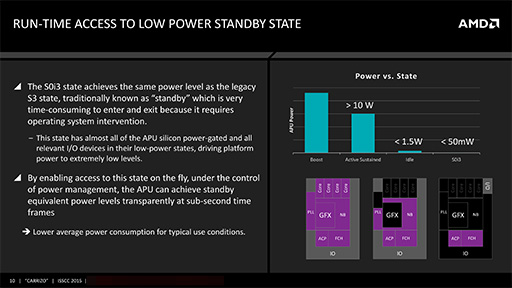

そのほかにも消費電力低減の工夫として,Carrizoでは「S0i3」(エスゼロアイスリー)と呼ばれる特殊な電力状態(ステート)がサポートされる。これは,PCで一般的な電力制御規格「ACPI」が定義するスリープモード「S3」に近い低消費電力状態でありながら,より短時間で通常の動作状態(S0)に復帰できるというステートだ。Intelはすでに「Bay Trail」ことAtom Z3700シリーズでS0i3をサポートしているので,AMDもCarrizoに同様の機能を取り入れてきたというところだろう。

Carrizoの場合,S0i3ではCPUコアやGPUコアに加えて,クロック生成回路「PLL」やチップセットのメモリコントローラ,I/O回路のほとんども停止することで,消費電力を50mW程度に抑えることが可能になるとしている。これがうまく機能するなら,Carrizo搭載の2-in-1デバイスやタブレット端末を持ち歩くときに,スリープさせた状態でも電力消費が減って,復帰させるときの動作も速くなると期待できそうだ。

|

H.265のハードウェア支援はデコードのみ

今回説明されたCarrizoの技術的な特徴は,半導体プロセスに関わるものがほとんどで,性能面や機能面での特徴はあまり説明されていない。とはいえ,いくつかの情報も小出しに公開されてはいる。

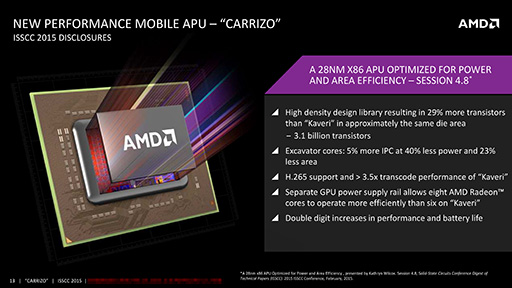

まず,トランジスタ数は約31億個で,Kaveriと同じダイサイズに29%多くのトランジスタを詰め込んだという。「処理能力とバッテリー駆動時間は2倍に向上」という,期待を持たせる文言もある。

Excavatorコアの性能面も少しだけ触れられており,Steamrollerコアに対しクロックあたりの性能(IPC:Instructions per Clock)が5%向上しているそうだ。IPCで5%という向上はわずかなものなので,単純なCPUコアの性能は,Kaveri世代と比べてあまり変わっていないということになると思われる。

一方で,GPUコアはGCN世代のものが8基と,Kaveri世代のA10-7850KやA10-7800と同じ数になっている。GPU、CPUともにCarrizoは電力効率の向上を主眼とした新製品になると言えそうだ。

|

ただ,少々残念な新情報もあった。スライドをよく見ると,「H.265がサポートされ,Kaveriと比べて動画のトランスコードが3.5倍高速」という記述があるのだが,質疑応答でH.265のサポートに関する質問が出たときにAMD側は,CarrizoのハードウェアによるH.265サポートがデコードのみで,エンコードはソフトウェアで行われると回答したのだ。

H.265はH.264と同等の画質を半分のビットレートで実現できるとされるコーデックである。NVIDIAはGeForce GTX 900シリーズでハードウェアH.265エンコーダを搭載することで,4K解像度で60fpsのビデオストリーミングを可能としているほか(関連記事),次世代のモバイル向けSoCである「Tegra X1」にもハードウェアH.265エンコーダを採用するなど,積極的なサポートを打ち出している。

それに比べると,CarrizoのH.265サポートがデコードのみというのは見劣りがする。Carrizoを使ったゲームストリーミングにH.265を使って高画質化するというのは,ちょっと難しいことになりそうだ。

半導体設計の改良に踏み込むことで実現されたCarrizoが,思惑どおりの性能とバッテリー駆動時間を実現できるのか。今後の情報に期待したい。

※お詫びと訂正

初出時,KaveriのGCNコアが6基としていましたが,8基の誤りです。お詫びして訂正いたします。

- 関連タイトル:

AMD A-Series(Carrizo)

AMD A-Series(Carrizo)

- この記事のURL: